Press release

Floating Point FFT IP-Core Lands on Scalable Video Platform from Sundance

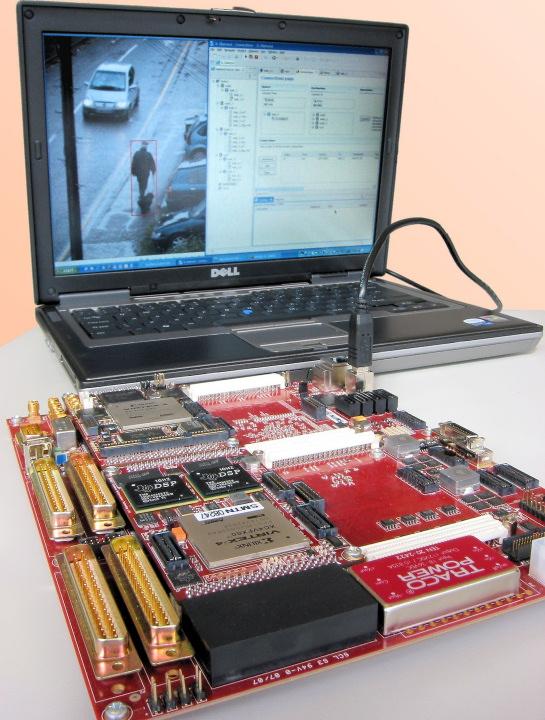

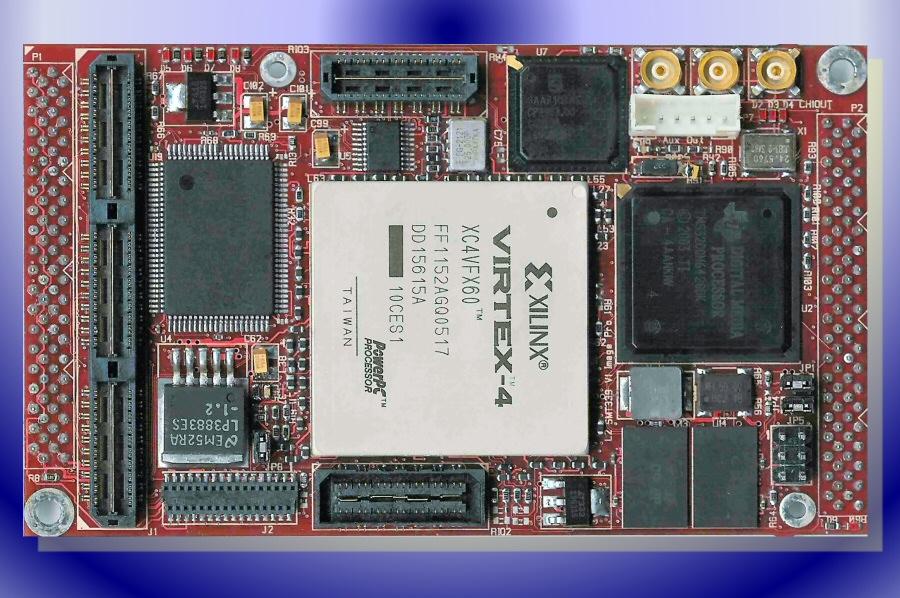

London, UK - October 1, 2007 -- The new Digital Video Infrastructure Platform (DVIP) from Sundance features from three to eleven fixed-point DSPs, equating to as much as 50000 MIPS (millions instructions per second). Where that is still not sufficient floating-point calculation power for the most demanding real-life application, the DVIP gets a helping hand from closely-coupled Xilinx® Virtex™-4 FX60 FPGAs.The FC100 Floating-point FFT IP-Core implemented in the FPGA is designed using a radix-32 architecture to make it flexible, portable, and use as few external memory resources as possible. Even then it’s possible to re-configure its complex data range from 256-point to 1M-point on-the-fly. It is ideally suited to high-powered image processing, radar or video encoding/decoding systems.

A single IP-Core will process 42 frames of a Video 2D transform each second on single 1024x1024 images and that will take less than 1/2 of the 128 XtremeDSP™ Slices available on a Virtex-4 FX60. The DVIP has three of these FPGAs as standard and up to four more FPGAs can be added.

The easiest way to visualize the power of combined fixed-point DSP and an FPGA enabled with the FC100 is a trip down memory lane, as Flemming Christensen, CTO of Sundance Multiprocessor Technology Ltd observes, "I can vividly remember when I was given an Intel 8087 math coprocessor in the early '80s to increase the performance of my Workstation PC. It was awesome. The 8087 could do 50000 FLOPS (floating point operations per second) whereas the DVIP can offer 50000 Mega FLOPS and still costs less than my old PC."

The FC100 is available in either VHDL source format or can be supplied as a 'task' to integrate into the Xilinx' 'System Generator for DSP' or The MathWork’s 'Simulink' tools. It has been verified to the IEEE-754 standard and comes with full simulation and implementation support. A bit-true model for performance evaluation is provided free of charge for evaluation purpose.

"Sundance has done an exceptional job integrating high performance DSP functions with Xilinx' FPGAs. By leveraging three high-performance Virtex-4 FX60 devices, the DVIP platform delivers impressive 2D transform performance," said Bruce Weyer, senior marketing director of the Programmable Solutions Group at Xilinx. "The development of the FFT IP-Core as a co-processor is the perfect technology match for demanding image processing solutions."

The DVIP is available now from a starting price of USD25000.00 in single quantities with OEM prices on request The FC100 IP-Core starts at USD10000.00 for the basic version.

About Sundance

Sundance leads the world in the design and manufacture of mixed COTS digital signal processing and FPGA architectures. Sundance modular and customizable COTS hardware and software systems are easy to reconfigure to suit all high-speed I/O and signal processing applications, enabling the rapid prototyping and development of embedded systems. Designers and manufacturers of wireless infrastructures, satellite communications, industrial signal processing, sonar/radar, software defined radio (SDR), multimedia and telecommunications, all depend on the flexibility of Sundance’s mixed DSP+FPGA platforms and systems to get their products to market – FAST!

Key design and manufacturing facilities are located in the UK, and mainland Europe and our worldwide network of agents – extending as far as Asia – provides quality service and support.

Web: sundance.com E-mail: DVIP@sundance.com

High res image can be downloaded from: clickintopr.com/editors/articleDetail.asp?pjID=525

More Information

USA, North Europe & Rest of the World

Sundance Multiprocessor Technology Ltd

Mr. Flemming Christensen

Chiltern House, Waterside, Chesham

, HP5 1PS, England

Tel: +44 (0)1494 793167

Fax: +44(0)1494 793168

Middle, South, East Europe

Sundance Italia S.R.L

Dr. Fabio Ancona

Corso XXV Aprile 55/3

16040 S. Salvatore di Cogorno (GE), Italy

Tel: +39 0185 385193

Fax: +39 0185 385370

Far East & Oceania

Sundance Asia Ltd

Pascal Coppens

1202, 12/F, Golden Star Building

20 Lockhart Road, Hong Kong

Tel: +852 3583 4283

Fax: +852 2810 4009

Web: www.sundance.com E-mail: DVIP@sundance.com

Mr. Flemming Christensen

Chiltern House, Waterside, Chesham

, HP5 1PS, England

Tel: +44 (0)1494 793167

Fax: +44(0)1494 793168

Middle, South, East Europe

Sundance Italia S.R.L

Dr. Fabio Ancona

Corso XXV Aprile 55/3

16040 S. Salvatore di Cogorno (GE), Italy

Tel: +39 0185 385193

Fax: +39 0185 385370

Far East & Oceania

Sundance Asia Ltd

Pascal Coppens

1202, 12/F, Golden Star Building

20 Lockhart Road, Hong Kong

Tel: +852 3583 4283

Fax: +852 2810 4009

Designers and manufacturers of wireless infrastructures, satellite communications, industrial signal processing, sonar/radar, software defined radio (SDR), multimedia and telecommunications, all depend on the flexibility of Sundance’s mixed DSP+FPGA platforms and systems to get their products to market – FAST!

This release was published on openPR.

Permanent link to this press release:

Copy

Please set a link in the press area of your homepage to this press release on openPR. openPR disclaims liability for any content contained in this release.

You can edit or delete your press release Floating Point FFT IP-Core Lands on Scalable Video Platform from Sundance here

News-ID: 29663 • Views: …

More Releases from Sundance Multiprocessor Technology Ltd

Sundance's Digital Video Platform Gets Helping Hand from Simulink HDL Coder from …

London, UK - August 21, 2007 -- The latest Digital Video Infrastructure Platform (DVIP) manufactured by Sundance Multiprocessor Technology Ltd., now supports Simulink HDL Coder from The MathWorks. This integration will enable embedded software engineers to target field-programmable gate-arrays (FPGAs) without detailed knowledge of programming such devices.

The DVIP from Sundance has been developed for the highest performance in high-definition broadcast systems or high-resolution image processing for medical applications. …

New Image Processing Development Platform Empowers System Designers

A new FPGA and DSP co-design platform for developing image processing equipment, the SMT339, has been launched by Sundance Multiprocessor Systems. At the core of the new board are the lightning fast Texas Instruments (TI) TMS320DM642 DSP-based digital media processor and Xilinx Virtex-4 FX-60 FPGA.

TI’s TMS320DM642 processor has been specially designed to optimise image processing performance with a stunning capability of 5760MIPS at a clock rate of 720MHz. …

More Releases for DVIP

Sundance's Digital Video Platform Gets Helping Hand from Simulink HDL Coder from …

London, UK - August 21, 2007 -- The latest Digital Video Infrastructure Platform (DVIP) manufactured by Sundance Multiprocessor Technology Ltd., now supports Simulink HDL Coder from The MathWorks. This integration will enable embedded software engineers to target field-programmable gate-arrays (FPGAs) without detailed knowledge of programming such devices.

The DVIP from Sundance has been developed for the highest performance in high-definition broadcast systems or high-resolution image processing for medical applications. …