Press release

Centellax, Inc. Releases SCS16000 Series of 16 GHz Stressed Clock Synthesizers

SANTA ROSA, CALIF.----February 1, 2011—Centellax announced today the release of their new SCS16000 series of compact 16 Gb/s stressed clock synthesizers. There are currently 2 models in the series:

SCS16000: 16 Gb/s Stressed clock Synthesizer with sinusoidal jitter injection capability

SCS16000J: 16 Gb/s Stressed Clock Synthesizer with two tone sinusoidal jitter, true random jitter injection, and spread spectrum clock modulation capabilities.

This series has been designed from the ground up optimized for signal integrity applications. The low intrinsic jitter synthesizer provides continuously settable clock frequencies from 0.5 to 16 GHz. Three outputs provide the main stressed clock, along with unstressed delayed and divided clocks derived from the main.

The base model, SCS16000, is ideal for many optical serial data applications, providing a single tone of sinusoidal jitter, settable over a wide range of frequencies and modulation depths. When used as a BERT clock source, the high resolution of the SJ enables precise jitter tolerance testing.

For the electrical serial data applications which require more complex “stress recipes”, the SCS16000J includes two independent sources of sinusoidal along with a broadband true random jitter sources. In addition, all three clock outputs can be modulated with spread spectrum, with a deviation settable up to 10,000 UI.

Series features include:

0.5-16.0 GHz operation

Internal sinusoidal jitter source

Fully programmable clock output parameters

Low intrinsic jitter

Main + Clean (non-jittered) divided and delayed outputs

Single port remote control through USB or GPIB

LabVIEW driver and SCPI command set for easy automation and test system integration

SCS16000J additionally includes:

Two independent SJ Sources

True Gaussian RJ Stress

Spread Spectrum Clock – standard

You can find more information about this product at: http://www.centellax.com/products/testmeas/SCS16000

Established in 2001, Centellax delivers affordable, high-performance test instruments, test accessories, and electrical components for high-speed communications and signal integrity applications worldwide. Corporate headquarters is located in Santa Rosa, CA, just 90 minutes north of San Francisco.

Centellax Headquarters

3843 Brickway Blvd., #100

Santa Rosa, CA 95403, USA

phone: +1.707.568.5900

sales: sales@centellax.com

This release was published on openPR.

Permanent link to this press release:

Copy

Please set a link in the press area of your homepage to this press release on openPR. openPR disclaims liability for any content contained in this release.

You can edit or delete your press release Centellax, Inc. Releases SCS16000 Series of 16 GHz Stressed Clock Synthesizers here

News-ID: 161202 • Views: …

More Releases from Centellax

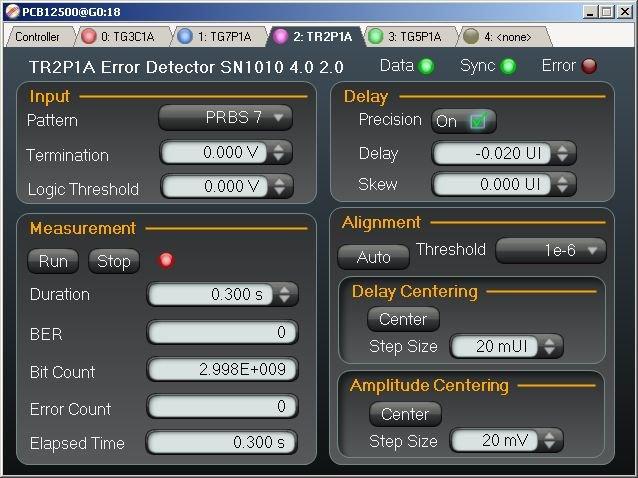

Centellax, Inc. Releases Windows-based Graphical User Interface for Multiple Ins …

SANTA ROSA, CALIF.----January 12, 2011—

Centellax announced today the release of their new Centellax Signal Integrity Studio (SIS) application, Version 1.0. SIS provides Centellax customers the ability to control multiple Centellax instruments through a Windows-based Graphical User Interface (GUI). This easy-to-understand interface allows for a more integrated and effective use of Centellax products. According to Steve Sekel, Centellax VP of Marketing, “SIS marks the beginning of the rich software applications that…

Centellax Partners with EDN China in live Webcast on Characterizing Crosstalk in …

Santa Rosa, Calif., November 10, 2010 -

Centellax announced today they will be partnering with EDN China to give a live webcast in Mandarin Chinese, on Characterizing Crosstalk in High-Density, High-Speed Backplanes. The webcast will outline the detrimental effects of crosstalk, discussing several methods of measuring crosstalk, and details the characterization of crosstalk in a high-density high-speed backplane. BER-based jitter measurements are used to quantify the impairment caused by near-end crosstalk…